IEEE TRANSACTIONS ON ELECTRON DEVICES

# Analyzing the Contact-Doping Effect in In<sub>2</sub>O<sub>3</sub> FETs: Unveiling the Mechanisms Behind the Threshold-Voltage Roll-Off in Oxide Semiconductor Transistors

Jian-Yu Lin<sup>®</sup>, *Graduate Student Member, IEEE*, Chang Niu<sup>®</sup>, *Member, IEEE*,

Zehao Lin<sup>®</sup>, *Graduate Student Member, IEEE*, Sumi Lee<sup>®</sup>,

Taehyun Kim, *Graduate Student Member, IEEE*, Jungho Lee, Chang Liu<sup>®</sup>, Juanjuan Lu, Haiyan Wang,

Muhammad Ashraful Alam<sup>®</sup>, *Fellow, IEEE*, Changwook Jeong<sup>®</sup>, *Member, IEEE*,

and Peide D. Ye<sup>®</sup>, *Fellow, IEEE*

Abstract—In this work, the contact-doping effect (CDE) and its impact on the threshold voltage  $(V_T)$  roll-off in indium oxide (In2O3) field-effect transistors (FETs) are systematically studied. By analyzing the long channel length  $(L_{ch})$  and short  $L_{ch}$  devices separately using a modified transfer length method (TLM),  $\Delta L$  can be extracted to quantify the CDE. The correlation between  $\Delta L$  and the  $\dot{L}_{ch}$  at which  $V_{T}$  roll-off occurs suggests that CDE may be a key factor contributing to the V<sub>T</sub> roll-off in In<sub>2</sub>O<sub>3</sub> transistors. Next, the underlying mechanisms of CDE are investigated. It is found that oxygen scavenging reactions (OSRs) during the deposition of source/drain (S/D) metals on the In<sub>2</sub>O<sub>3</sub> channel is one of the reasons behind CDE. S/D metals can scavenge oxygen atoms from In<sub>2</sub>O<sub>3</sub>, creating oxygen vacancies and increasing the carrier density near the S/D regions. Additionally, the Schottky barrier height  $(\Phi_{SB})$  of metal/ $\ln_2 O_3$  contacts might also influence the CDE: a positive  $\Phi_{SB}$  depletes carriers, while a negative  $\Phi_{SB}$ accumulates them in the In<sub>2</sub>O<sub>3</sub> channel under the S/D. This study provides a new approach to investigating CDE and highlights its critical role in understanding the  $V_T$  roll-off in oxide semiconductor (OS) transistors.

Received 7 March 2025; revised 17 April 2025; accepted 21 April 2025. This work was supported by the National Science Foundation (NSF) Future of Semiconductors (FuSe2), Semiconductor Research Corporation (SRC) Global Research Collaboration (GRC), Samsung Electronics Inc. The work of Changwook Jeong was supported by the Technology Innovation Program funded by the Ministry of Trade, Industry and Energy (MOTIE), Korea, under Grant RS-2023-00231956. The review of this article was arranged by Editor J.-S. Park. (Corresponding author: Peide D. Ye.)

Jian-Yu Lin, Chang Niu, Zehao Lin, Sumi Lee, Muhammad Ashraful Alam, and Peide D. Ye are with the Elmore Family School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA (e-mail: yep@purdue.edu).

Taehyun Kim, Jungho Lee, and Changwook Jeong are with the Graduate School of Semiconductor Materials and Devices Engineering, Ulsan National Institute of Science and Technology, Ulsan 44919, Republic of Korea.

Chang Liu, Juanjuan Lu, and Haiyan Wang are with the School of Materials Engineering, Purdue University, West Lafayette, IN 47907 USA.

Digital Object Identifier 10.1109/TED.2025.3564265

Index Terms—contact-doping effect (CDE), indium oxide  $(In_2O_3)$ , oxygen scavenging reaction (OSR), Schottky barrier height, threshold voltage roll-off.

### I. INTRODUCTION

NDIUM oxide (In<sub>2</sub>O<sub>3</sub>) based oxide semiconductor (OS) field-effect transistors (FETs) have gained increasing research attention in recent years due to their promising application for monolithic 3-D integration (M3DI) [1], [2], [3], [4], [5], [6], [7], [8], [9], [10], [11], [12], [13], [14], [15]. The concept of M3DI is to directly grow and fabricate semiconductor devices on top of an already processed front-end-of-line (FEOL) layer, such as silicon logic devices or chips [1], [16]. This approach enhances chip performance in two ways: *more Moore* and *more than Moore*. First, M3DI increases the device density per area by stacking additional transistors above the FEOL layer (*More Moore*) [7], [14]. Second, it enables heterogeneous integration of various semiconductor devices—such as radio frequency (RF) [17], [18], memory [15], and power devices [19]—to enhance chip functionality (*More than Moore*).

A key challenge in achieving M3DI is the strict back-end-of-line (BEOL) thermal budget, which typically requires processing temperatures below 400 °C [1]. Fortunately, OSs can be deposited and further processed at temperatures below this limit, making them excellent candidates for M3DI [5]. Among various OS FETs, atomic-layer-deposited (ALD)  $In_2O_3$  FETs offer several advantages, including excellent conformality and uniformity on 3-D structures [5], high electron mobility of 152 cm²/(V·s) [20], ultrahigh ON-current ( $\sim$ 20 mA/ $\mu$ m) in gate-all-around structure [21], good reliability [13], and ultralow contact resistance ( $R_C$ ) of 23.4  $\Omega \cdot \mu$ m, approaching the quantum limit of metal/semiconductor contacts [8], [22].

The channel length  $(L_{ch})$  dependent threshold voltage  $(V_T)$ —specifically, the  $V_T$  roll-off phenomenon as the  $L_{ch}$

decreases—has been widely reported in In<sub>2</sub>O<sub>3</sub> and doped-In<sub>2</sub>O<sub>3</sub> [e.g., InSnO, InZnO (IZO), InGaO (IGO), and InGaZnO (IGZO)] FETs [4], [6], [9], [12], [18], [22], [23], [24], [25], [26], [27]. While many studies have investigated methods to mitigate  $V_{\rm T}$  roll-off, relatively few have explored the underlying mechanisms responsible for the  $L_{ch}$ -dependent  $V_{T}$  shifts in In<sub>2</sub>O<sub>3</sub>-based FETs [23]. A common assumption is that this roll-off stems from the short-channel effect (SCE), which occurs when electrostatic control of gate to channel weakens as the source/drain (S/D) spacing or  $L_{ch}$  shrinks. However, most In<sub>2</sub>O<sub>3</sub>-based FETs are thin-film transistors (TFTs) with channel thickness far below 10 nm [3], [4], [5], [6], [7], [8], [9], [10], [11], [12], [18], [26]. In such ultrathin channels, strong gate control should effectively suppress the traditional SCE in the investigated  $L_{\rm ch}$  range ( $\geq$ 40 nm). This suggests that the observed V<sub>T</sub> roll-off in In<sub>2</sub>O<sub>3</sub>-based TFTs is driven by mechanisms beyond conventional SCE.

In this work, we propose that the contact-doping effect (CDE) is responsible for the  $V_{\rm T}$  roll-off in  $\rm In_2O_3$  FETs. Using a modified transfer length method (TLM), we systematically investigate and verify the relationship between CDE and  $V_{\rm T}$  roll-off. Additionally, by varying S/D metal materials, we explore the physical mechanisms underlying CDE. This research offers new insights into CDE and its influence on  $V_{\rm T}$  roll-off, emphasizing its significance in the design and optimization of aggressively scaled OS transistors.

## II. EXPERIMENTS AND SIMULATIONS

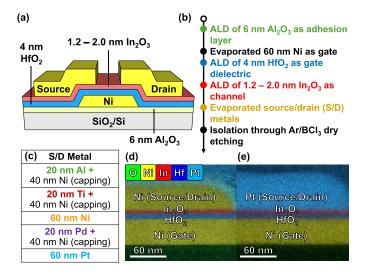

Fig. 1(a) illustrates the schematic of the back-gate (BG) In<sub>2</sub>O<sub>3</sub> transistors analyzed in this study, and Fig. 1(b) outlines the fabrication process. The process began with the deposition of 6 nm Al<sub>2</sub>O<sub>3</sub> adhesion layer via ALD at 175 °C on SiO<sub>2</sub>/Si substrate, followed by 60 nm Ni BG deposited through electron-beam evaporation. Next, 4 nm HfO2 gate dielectric was deposited by ALD at 200 °C. In<sub>2</sub>O<sub>3</sub> with channel thickness  $(T_{ch})$  ranging from 1.2 to 2.0 nm was used as transistor channel and was grown by ALD at 225 °C. Various metals were then deposited by electron-beam evaporation to serve as the S/D electrodes, as listed in Fig. 1(c). Different S/D materials were employed to investigate the CDE in In<sub>2</sub>O<sub>3</sub> transistors. Finally, channel isolation and the definition of transistor channel width  $(W_{ch})$  of 1  $\mu$ m were achieved through inductively coupled plasma (ICP) etching using Ar/BCl<sub>3</sub> plasma. For the ALD processes above, Al(CH<sub>3</sub>)<sub>3</sub> (TMA), [(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Hf (TDMAHf), (CH<sub>3</sub>)<sub>3</sub>In (TMIn), and H<sub>2</sub>O were used as Al, Hf, In, and O precursors, respectively. Fig. 1(d) shows a cross-sectional scanning transmission electron microscopy (STEM) image with energy-dispersive X-ray spectroscopy (EDS) elemental mapping of an In<sub>2</sub>O<sub>3</sub> FET with Ni as the S/D material, while Fig. 1(e) presents the corresponding image for a device with Pt as S/D.

Electrical characterizations were conducted at room temperature in a Cascade probe station under an  $N_2$  ambient using the Keysight B1500A system. The  $V_T$  of the devices was determined via the linear extrapolation method based on their transfer characteristics.

To investigate the oxygen interstitial formation energy for different metals, *ab initio* calculations were performed using the QuantumATK software with the GGA-PBE functional and

Fig. 1. (a) Schematic device structure of BG  $In_2O_3$  transistors. (b) Fabrication process flow of BG  $In_2O_3$  FETs. (c) List of S/D metals used in this work. Different S/D metals were utilized to study the CDE in  $In_2O_3$  devices. Cross-sectional STEM image with EDS elemental mappings of  $In_2O_3$  FETs with (d) Ni as S/D and (e) Pt as S/D.

PseudoDojo basis sets. Oxygen atoms were placed at interstitial sites, identified based on the lowest energy configuration.

### III. RESULTS AND DISCUSSION

### A. Quantification of the CDE

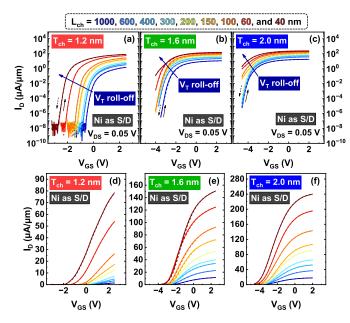

Fig. 2 presents the transfer characteristics of  $In_2O_3$  FETs with different  $L_{ch}$ , Ni as the S/D metal, and  $T_{ch} = 1.2$ , 1.6, and 2.0 nm. Noticeable  $V_T$  roll-off is observed as the  $L_{ch}$  decreases from 1000 to 40 nm across all  $T_{ch}$  conditions. To elaborate, for  $T_{ch} = 1.2$  and 1.6 nm, the  $I_D$ – $V_{GS}$  curves exhibit a negative shift when  $L_{ch}$  falls below 600 nm [Fig. 2(a) and (b)]. For  $T_{ch} = 2.0$  nm, a similar leftward shift is observed when  $L_{ch}$  is reduced to below 200 nm [Fig. 2(c)]. The  $V_T$  roll-off observed in Fig. 2 is unlikely to be caused by the traditional SCE. SCE can be quantified by the natural length theory of MOSFETs [28], [29]. The natural length ( $\lambda$ ) of silicon-oninsulator (SOI) MOSFETs—whose structure is similar to BG  $In_2O_3$  FETs—is given by

$$\lambda = \sqrt{\frac{\varepsilon_{\rm ch}}{\varepsilon_{\rm ox}} \cdot T_{\rm ch} \cdot T_{\rm ox}} \tag{1}$$

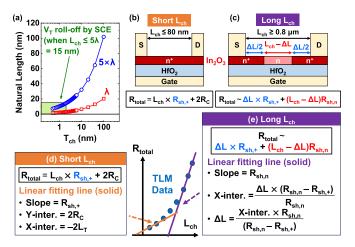

where  $\varepsilon_{ch}$  is the dielectric constant of the channel material (In<sub>2</sub>O<sub>3</sub> with  $\varepsilon_{ch} = 8.9$  [3]),  $\varepsilon_{ox}$  is the dielectric constant of the gate oxide (HfO<sub>2</sub> with  $\varepsilon_{\rm ox} \sim$  8.6, calculated based on the measured gate oxide capacitance of  $1.9 \times 10^{-6}$  F/cm<sup>2</sup>),  $T_{\rm ch}$ is the channel thickness, and  $T_{ox}$  is the gate oxide thickness  $(T_{\rm ox} = 4.0 \text{ nm})$ . For our In<sub>2</sub>O<sub>3</sub> devices with  $T_{\rm ch} = 1.2$ –2.0 nm,  $\lambda$  values are calculated to be 2–3 nm using (1), as shown in Fig. 3(a). Given that SCE should only become significant when  $L_{\rm ch} \leq 5 \times \lambda = 10\text{--}15$  nm [29], the In<sub>2</sub>O<sub>3</sub> transistors in this study should remain unaffected by the SCE since the gate control over the channel center is still stronger than the control from S/D. However, the calculated 5  $\times$   $\lambda$  values contradict our experimental observations of  $V_T$  roll-off happening at  $L_{ch}$ below 600 nm (Fig. 2). This discrepancy suggests that the roll-off is not caused by SCE but rather by other reasons, such as CDE.

Fig. 2. Transfer characteristics of  $\ln_2 O_3$  transistors with Ni as S/D metal, channel length  $(L_{\rm ch})=1~\mu{\rm m}-40$  nm, and channel thickness  $(T_{\rm ch})$  of 1.2 nm [(a):  $I_{\rm D}$  in log scale; (d):  $I_{\rm D}$  in linear scale], 1.6 nm [(b):  $I_{\rm D}$  in log scale; (e):  $I_{\rm D}$  in linear scale], and 2.0 nm [(c):  $I_{\rm D}$  in log scale; (f):  $I_{\rm D}$  in linear scale]. Solid lines indicate  $V_{\rm GS}$  sweeping forward, while dashed lines represent  $V_{\rm GS}$  sweeping backward.

It is suspected that the carrier density (i.e., electron density) within the In<sub>2</sub>O<sub>3</sub> channel is non-uniform, with a higher carrier concentration near the S/D contacts compared to the channel center [Fig. 3(c)]. This phenomenon is referred to as CDE, as if the S/D contacts effectively increase the carrier density of the In<sub>2</sub>O<sub>3</sub> channel under them. The non-uniform carrier distribution caused by CDE is illustrated in Fig. 3(b) and (c). Fig. 3(c) shows a schematic carrier density profile for In<sub>2</sub>O<sub>3</sub> transistors with long  $L_{\rm ch}$  ( $\geq 0.8~\mu {\rm m}$ ), featuring  $n^+$  (high electron density) regions near the S/D and an n (medium electron density) region at the channel center.  $\Delta L$  is defined as the length of the  $n^+$  regions extending into the channel, with  $\Delta L/2$  contributed by the source and  $\Delta L/2$  by the drain. When  $L_{\rm ch}$  is sufficiently short ( $\leq 80$  nm), the  $n^+$  regions from the S/D merge, as shown in Fig. 3(b). To extract the  $\Delta L$  and quantify the CDE, a modified TLM is developed based on Fig. 3(b) and (c). From the long  $L_{\rm ch}$  ( $\geq 0.8~\mu {\rm m}$ ) devices, the total resistance ( $R_{\text{total}}$ ) of the transistors can be written as

$$R_{\text{total}} \sim \Delta L \times R_{\text{sh},+} + (L_{\text{ch}} - \Delta L) R_{\text{sh},n}$$

(2)

where  $R_{\rm sh,+}$  is the sheet resistance of the  $n^+$  region and  $R_{\rm sh,n}$  is the sheet resistance of the n region. Using (2),  $R_{\rm sh,n}$  can be extracted from the slope of the linear fitting lines in the long  $L_{\rm ch}$  regime TLM analysis [Fig. 3(e)]. As for the short  $L_{\rm ch}$  ( $\leq$ 80 nm) devices, the  $R_{\rm total}$  is given by

$$R_{\text{total}} = L_{\text{ch}} \times R_{\text{sh},+} + 2R_C. \tag{3}$$

Utilizing (3),  $R_{\text{sh},+}$  can be determined from the slopes and  $R_C$  can be calculated from the *Y*-intercept of the linear fitting lines in the short  $L_{\text{ch}}$  regime [Fig. 3(d)]. By combining the  $R_{\text{sh},n}$  and  $R_{\text{sh},+}$ ,  $\Delta L$  can be calculated using the following

(a) Calculated natural length ( $\lambda$ ) as a function of  $T_{ch}$ . When  $L_{\rm ch}$  is smaller than 5  $\times$   $\lambda$ ,  $V_{\rm T}$  roll-off due to SCE is expected. For  $T_{\text{ch}}$  below 10 nm, the calculated  $\lambda$  remains under 6.5 nm, with 5  $\times$  $\lambda \leq 33$  nm. (b) and (c) Illustrate schematic cross sections of  $In_2O_3$ transistors, showing carrier density profiles along the Lch direction for short  $L_{ch}$  ( $\leq$ 80 nm) and long  $L_{ch}$  ( $\geq$ 0.8  $\mu$ m) devices, respectively. The  $n^+$  region represents a high carrier density area, while the n region corresponds to a medium carrier density area.  $\Delta L$  denotes the length of the  $n^+$  regions extending into the channel.  $R_{\text{total}}$  is the total channel resistance, with  $R_{sh,+}$  and  $R_{sh,n}$  representing the sheet resistances of the  $n^+$  and n regions, respectively. If the carrier density in the  $\ln_2 O_3$ channel is nonuniform, the TLM analysis of Rtotal-Lch data can be divided into two parts: (d) short  $L_{ch}$  segment, corresponding to the case of (b); (e) long  $L_{ch}$  segment, corresponding to the case of (c). Y-inter. and X-inter. represent the Y- and X-intercepts of the linear fitting lines, respectively.  $R_C$  is the contact resistance, and  $L_T$  is the transfer length.

equation derived from (2):

$$\Delta L = \frac{X \text{-inter.} \times R_{\text{sh},n}}{\left(R_{\text{sh},n} - R_{\text{sh},+}\right)} \tag{4}$$

where X-inter. represents the X-intercept of the linear fitting lines in the long  $L_{\rm ch}$  regime TLM analysis [Fig. 3(e)]. It should be noted that in the analysis of Fig. 3(b)–(e), the transition between  $n^+$  and n regions is approximated as a step change to simplify the calculations and TLM analysis. A gradual transition from  $n^+$  to n regions could be present, which may need to be considered for a more precise estimation of the CDE.

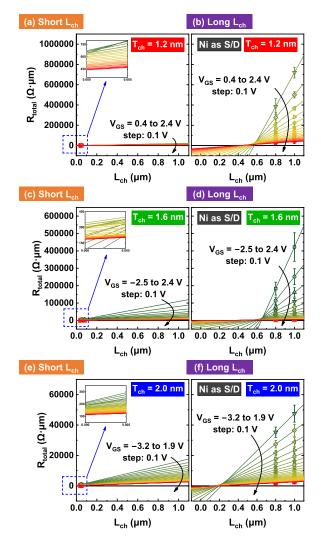

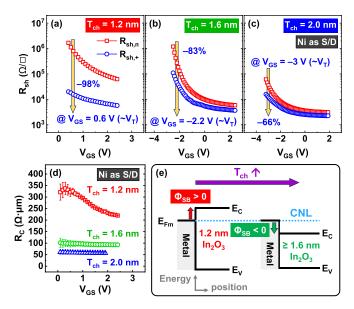

Fig. 4 presents the TLM analysis of total resistance  $(R_{\text{total}})$ as a function of  $L_{ch}$  for  $In_2O_3$  transistors with various  $T_{ch}$ . To accurately quantify the CDE, each set of  $R_{\text{total}}$ - $L_{\text{ch}}$  data is analyzed at the same  $V_{GS}$  rather than the same  $V_{GS}$ - $V_{T}$ . While adjusting  $R_{\text{total}}$ - $L_{\text{ch}}$  data based on  $V_{\text{GS}}$ - $V_{\text{T}}$  for each  $L_{\text{ch}}$  is a common practice to improve TLM linear fitting, particularly when  $V_{\rm T}$  depends on  $L_{\rm ch}$  [8], [25], [30], such normalization would exclude the information about CDE, as CDE itself is the potential cause of the  $V_T$  roll-off in  $In_2O_3$  devices. For each  $T_{\rm ch}$ , the  $R_{\rm total}$ – $L_{\rm ch}$  data at a given  $V_{\rm GS}$  is divided into two segments: short  $L_{ch}$  (40-80 nm) [Fig. 4(a), (c), and (e)] and long  $L_{ch}$  (0.8–1.0  $\mu$ m) [Fig. 4(b), (d), and (f)], which are then analyzed using linear regression. According to the proposed TLM framework [Fig. 3(d) and (e)],  $R_{sh,+}$  and  $R_{sh,n}$  are extracted from the short- and long- $L_{ch}$  regimes, respectively, as shown in Fig. 5(a)-(c). The extracted  $R_{sh,+}$  values are

Fig. 4. TLM analysis of total resistance  $(R_{\text{total}})$  versus  $L_{\text{ch}}$  for  $\ln_2 O_3$  FETs with different  $T_{\text{ch}}$  values: (a) and (b) 1.2 nm, (c) and (d) 1.6 nm, and (e) and (f) 2.0 nm. For each  $T_{\text{ch}}$ , the  $R_{\text{total}}-L_{\text{ch}}$  data is divided into two regions: short  $L_{\text{ch}}$  (40–80 nm) in (a), (c), and (e); long  $L_{\text{ch}}$  (0.8–1  $\mu$ m) in (b), (d), and (f). Symbols represent experimental data, averaged over at least five devices. Solid lines indicate the linear fitting of the data. For the short  $L_{\text{ch}}$  regime [(a), (c), and (e)],  $R_{\text{sh},\text{h}}$  and  $R_{C}$  are extracted using the equations in Fig. 3(d) For the long  $L_{\text{ch}}$  regime [(b), (d), and (f)],  $R_{\text{sh},\text{h}}$  is extracted using the equation in Fig. 3(e).

consistently lower than  $R_{\text{sh},n}$  across all  $T_{\text{ch}}$ , confirming the presence of a non-uniform carrier density in the  $\text{In}_2\text{O}_3$  channel.

Fig. 5(d) shows the extracted  $R_C$  as a function of  $V_{\rm GS}$ , revealing that the  $R_C$  decreases as the  $T_{\rm ch}$  increases. This behavior is linked to the transition from a positive to a negative Schottky barrier height ( $\Phi_{\rm SB}$ ) at the metal/In<sub>2</sub>O<sub>3</sub> contact [25], [31], as illustrated in Fig. 5(e). The quantum confinement effect (QCE) modifies the band structure of In<sub>2</sub>O<sub>3</sub> as the  $T_{\rm ch}$  becomes thinner [3], [25]. For instance, when  $T_{\rm ch}$  is reduced from 1.6 to 1.2 nm, the QCE shifts the conduction band minimum ( $E_{\rm C}$ ) upward, moving it above the charge neutrality level (CNL) of In<sub>2</sub>O<sub>3</sub>. Due to strong Fermi-level pinning at the metal/In<sub>2</sub>O<sub>3</sub> interface, the metal Fermi level ( $E_{\rm FM}$ ) remains close to the CNL of In<sub>2</sub>O<sub>3</sub> [25]. Consequently, the alignment between  $E_{\rm C}$  and CNL (which closely matches  $E_{\rm FM}$ ) dictates the value of  $\Phi_{\rm SB}$ . If  $E_{\rm C}$  is above CNL (as in the case of  $T_{\rm ch}$

Fig. 5. Extracted  $R_{\mathrm{sh},n}$  and  $R_{\mathrm{sh},+}$  as a function of  $V_{\mathrm{GS}}$  for  $\ln_2\mathrm{O_3}$  FETs with  $T_{\mathrm{ch}}$  of (a) 1.2 nm, (b) 1.6 nm, and (c) 2.0 nm. The  $R_{\mathrm{sh},n}$  and  $R_{\mathrm{sh},+}$  near  $V_{\mathrm{GS}}{\sim}V_{\mathrm{T}}$  ( $V_{\mathrm{T}}$  from the devices with  $L_{\mathrm{ch}}=1~\mu\mathrm{m}$ ) are highlighted in orange arrows to emphasize their differences. (d) Extracted  $R_{\mathrm{C}}$  as a function of  $V_{\mathrm{GS}}$  for  $\ln_2\mathrm{O_3}$  transistors with  $T_{\mathrm{ch}}$  ranging from 1.2 to 2.0 nm.  $R_{\mathrm{C}}$  are extracted based on the short  $L_{\mathrm{ch}}$  TLM analysis. (e) Schematic band diagrams of metal/ $\ln_2\mathrm{O_3}$  contacts for different  $\ln_2\mathrm{O_3}$  thicknesses.  $E_{\mathrm{C}}$ : conduction band minimum, CNL: CNL of  $\ln_2\mathrm{O_3}$ , and  $E_{\mathrm{FM}}$ : metal Fermi level.

1.2 nm), a positive  $\Phi_{\rm SB}$  forms at the metal/In<sub>2</sub>O<sub>3</sub> contact. Conversely, when  $E_{\rm C}$  falls below CNL (as seen for  $T_{\rm ch} \geq$  1.6 nm),  $\Phi_{\rm SB}$  becomes negative. This transition in  $\Phi_{\rm SB}$  with increasing  $T_{\rm ch}$  from 1.2 nm to above 1.6 nm has been studied and corroborated in our earlier work [25].

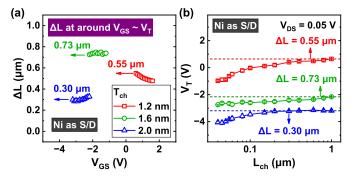

Fig. 6(a) presents the extracted  $\Delta L$  as a function of  $V_{GS}$ , calculated using (4). The  $\Delta L$  values at  $V_{\rm GS} \sim V_{\rm T}$ , ranging from 0.30 to  $0.73 \mu m$ , are highlighted for reference. Fig. 6(b) shows the relationship between  $V_{\rm T}$  and  $L_{\rm ch}$  for different  $T_{\rm ch}$ . As previously discussed in Fig. 2, all devices exhibit significant  $V_{\rm T}$ roll-off, even when  $L_{\rm ch}$  remains larger than  $5 \times \lambda$ . Notably, the  $L_{\rm ch}$  at which  $V_{\rm T}$  roll-off begins aligns well with the extracted  $\Delta L$  values at  $V_{\rm GS} \sim V_{\rm T}$  [Fig. 6(a) and (b)], substantiating the impact of the CDE on  $V_T$  roll-off. The relatively large  $\Delta L$ values further explain why  $V_{\rm T}$  roll-off occurs even when  $L_{\rm ch}$ is much greater than the natural length (5  $\times$   $\lambda$  = 10–15 nm) of the transistors. When  $L_{\rm ch} > \Delta L$ , reducing  $L_{\rm ch}$  has minimal impact on  $V_{\rm T}$ , as the carrier density at the channel center stays unaffected by the  $n^+$  regions extending from the S/D contacts [like Fig. 3(c)]. However, when  $L_{\rm ch} \leq \Delta L$ , the  $n^+$  regions from the S/D begin to merge, increasing the carrier density at the channel center [like Fig. 3(b)]. This results in a negative shift of  $V_T$  and a pronounced  $V_T$  roll-off as  $L_{ch}$  decreases.

# B. Mechanisms Behind the CDE

The high carrier density  $n^+$  regions beneath the S/D electrodes, referred to as the CDE, have been identified as a key factor contributing to the  $V_{\rm T}$  roll-off of  ${\rm In_2O_3}$  FETs in the previous section. The remaining questions are: what causes this CDE in  ${\rm In_2O_3}$  transistors, and why do S/D metals increase the carrier density in the underlying  ${\rm In_2O_3}$ ? In this work,

Fig. 6. (a) Extracted  $\Delta L$  as a function of  $V_{\rm GS}$  for  $\ln_2 O_3$  FETs with  $T_{\rm ch}$  ranging from 1.2 to 2.0 nm. The  $\Delta L$  values at  $V_{\rm GS} \sim V_{\rm T}$  are highlighted for reference. (b) Linearly extrapolated  $V_{\rm T}$  as a function of  $L_{\rm ch}$ . Each data point represents the average of at least five devices. All  $T_{\rm ch} \ln_2 O_3$  FETs exhibit a clear  $V_{\rm T}$  roll-off phenomenon, even when  $L_{\rm ch}$  is still significantly larger than  $5 \times \lambda$ , suggesting that the CDE might influence the  $V_{\rm T}$  behavior. The  $\Delta L$  values at  $V_{\rm GS} \sim V_{\rm T}$  are marked in the figure and show good consistency with the  $L_{\rm ch}$  at which the  $V_{\rm T}$  roll-off begins.

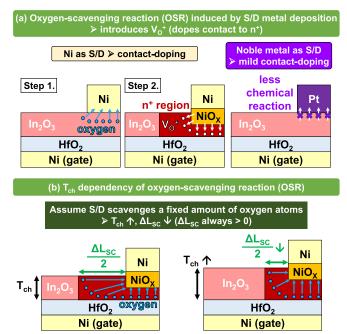

we propose two mechanisms that may contribute to the contact doping in In<sub>2</sub>O<sub>3</sub> FETs. The first one is oxygen-scavenging reactions (OSR) at the metal/In<sub>2</sub>O<sub>3</sub> S/D contacts (Fig. 7), and the second one is the change in the sign of the  $\Phi_{SB}$ at metal/In<sub>2</sub>O<sub>3</sub> interface (Fig. 8). These mechanisms provide insight into why CDE, quantified by  $\Delta L$ , depends on the  $T_{\rm ch}$ of In<sub>2</sub>O<sub>3</sub>, as shown in Fig. 6(a). When Ni is deposited as the S/D metal, it may react with In<sub>2</sub>O<sub>3</sub>, scavenging oxygen atoms from the channel. This scavenging process generates oxygen vacancies  $(V_0^+)$  in the  $In_2O_3$  channel [Fig. 7(a)]. Since  $V_0^+$ acts as a shallow donor and directly correlates with the carrier density in doped In<sub>2</sub>O<sub>3</sub> (such as IGZO and ITO) and pure  $In_2O_3$  [4], [6], [9], [32], the introduction of  $V_0^+$  via OSR increases electron density, forming  $n^+$  regions near the S/D contacts. The length of the  $n^+$  region induced by OSR is denoted as  $\Delta L_{SC}$ , as illustrated in Fig. 7(b). For the same type of S/D metal, assuming a consistent amount of oxygen is scavenged from the  $In_2O_3$  channel, the product  $\Delta L_{SC} \times T_{ch}$  which is proportional to the total number of oxygen atoms involved in the scavenging reactions—should remain similar. Consequently, in thinner  $T_{\rm ch}$  devices,  $\Delta L_{\rm SC}$  must be longer than in thicker  $T_{ch}$  transistors to provide sufficient oxygen atoms for the scavenging reaction.

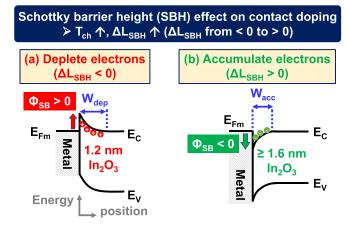

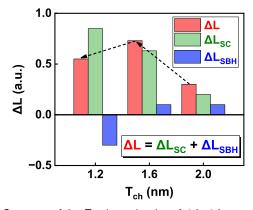

The  $\Phi_{SB}$  at the metal/ $In_2O_3$  interface also influences the carrier density beneath the S/D contacts, as illustrated in Fig. 8. When  $\Phi_{SB} > 0$ , electrons near the contact are depleted due to the upward band bending at  $V_{GS} = V_{T}$ , forming a depletion region with width =  $W_{\text{dep}}$  [Fig. 8(a)]. This depletion effect counteracts the OSR-induced carrier increase, potentially leading to  $n^-$  rather than  $n^+$  regions in  $In_2O_3$ . Conversely, when  $\Phi_{SB}$  < 0, the metal/In<sub>2</sub>O<sub>3</sub> interface accumulates electrons due to downward band bending [22], creating an accumulation region with width =  $W_{\rm acc}$  [Fig. 8(b)]. Defining  $\Delta L_{\rm SBH}$  as the length of the  $n^+$  region induced by the  $\Phi_{SB}$  from S/D, a positive  $\Phi_{SB}$  at  $T_{ch} = 1.2$  nm results in  $\Delta L_{SBH} < 0$ , reducing the  $n^+$  region length generated from OSR. Meanwhile, a negative  $\Phi_{\rm SB}$  at  $T_{\rm ch} \geq 1.6$  nm leads to  $\Delta L_{\rm SBH} > 0$ , expanding the  $n^+$ region. The overall dependencies of  $\Delta L$ ,  $\Delta L_{SC}$ , and  $\Delta L_{SBH}$ on  $T_{ch}$  are summarized in Fig. 9, where  $\Delta L$  is determined by

Fig. 7. (a) Schematic illustration of the oxygen-scavenging reaction (OSR) induced by the S/D metal. When a metal such as Ni is deposited on  $\rm In_2O_3$ , it may react with  $\rm In_2O_3$  and scavenge oxygen atoms from the channel. Oxygen vacancies ( $V_O^+$ ) are generated during the OSR process. In contrast, using noble metals like Pt as S/D can suppress the OSR. (b) Schematic representation of the  $T_{\rm Ch}$ -dependent OSR effect, where  $\Delta L_{\rm SC}/2$  denotes the length of the  $n^+$  region formed due to the OSR from the source or drain metal. The total length of  $n^+$  region from S/D is  $\Delta L_{\rm SC}$ .

the sum of  $\Delta L_{\rm SC}$  and  $\Delta L_{\rm SBH}$  ( $\Delta L = \Delta L_{\rm SC} + \Delta L_{\rm SBH}$ ). Fig. 9 explains the  $\Delta L$ - $T_{\rm ch}$  relationship observed in Fig. 6. Note that the impact of  $\Phi_{\rm SB}$  on  $\Delta L$  is constrained by the small values of  $W_{\rm dep}$  and  $W_{\rm acc}$ , leading to a relatively minor  $|\Delta L_{\rm SBH}|$ . As a result, the  $\Phi_{\rm SB}$  effect on  $\Delta L$  and  $V_{\rm T}$  may be overshadowed unless OSR at the S/D contact is mitigated—an aspect that will be further explored in Figs. 10 and 11.

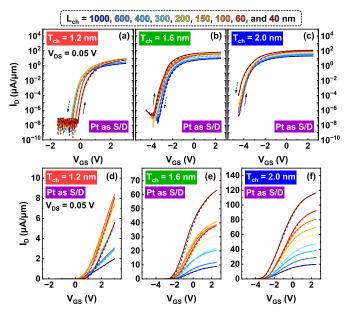

Since OSR plays a critical role in the CDE, there are two effective strategies to reduce the OSR and improve the  $V_{\rm T}$ roll-off caused by the CDE in In<sub>2</sub>O<sub>3</sub> FETs. These strategies also reinforce the idea that OSR is a key contributor to CDE and  $V_T$  roll-off. The first approach is using  $O_2$  annealing or  $O_2$  plasma treatments to reduce the  $V_O^+$  generated by the OSR, a method that has been well-studied in our previous works [4], [24]. The second approach involves replacing the S/D metals with noble metals, such as Pt, which should experience less OSR with In<sub>2</sub>O<sub>3</sub> [as illustrated in Fig. 7(a)]. Therefore, noble metals are expected to alleviate the  $V_T$  roll-off issue and reduce the CDE. Fig. 10 presents the transfer characteristics of In<sub>2</sub>O<sub>3</sub> FETs with different  $L_{\rm ch}$ ,  $T_{\rm ch}=1.2$ , 1.6, and 2.0 nm, and Pt as the S/D metal. Fig. 11 shows the  $V_T$ - $L_{ch}$  dependencies extracted from the  $I_D$ – $V_{GS}$  curves in Fig. 10. When compared to devices with Ni as S/D [Fig. 2 for transfer curves and Fig. 6(b) for  $V_T$ – $L_{ch}$  dependency],  $In_2O_3$  FETs with Pt as the S/D metal clearly exhibits improved  $V_{

m T}$  roll-off as the  $L_{

m ch}$ decreases. This supports the hypothesis that OSR at the S/D interfaces contributes significantly to the  $V_T$  roll-off and CDE in  $In_2O_3$  transistors.

Fig. 8. Schematic band diagrams of metal/ln<sub>2</sub>O<sub>3</sub> contacts for (a)  $T_{\rm ch}=1.2$  nm (with  $\Phi_{\rm SB}>0$ ) and (b)  $T_{\rm ch}\geq 1.6$  nm (with  $\Phi_{\rm SB}<0$ ) at  $V_{\rm GS}=V_{\rm T}$ . The length of the  $n^+$  regions induced by the  $\Phi_{\rm SB}$  at the metal/ln<sub>2</sub>O<sub>3</sub> contacts is denoted as  $\Delta L_{\rm SBH}$ . A positive  $\Phi_{\rm SB}$  depletes electrons at the interface, creating a depletion region with a width  $W_{\rm dep}$ , which counteracts the carrier increase caused by OSR at the S/D contacts ( $\Delta L_{\rm SBH}<0$ ). In contrast, a negative  $\Phi_{\rm SB}$  leads to electron accumulation, contributing to an accumulation width  $W_{\rm acc}$ , which further intensifies the CDE in the  $\ln_2{\rm O_3}$  channel ( $\Delta L_{\rm SBH}>0$ ). Since  $\ln_2{\rm O_3}$  is an n-type semiconductor,  $W_{\rm acc}$  is inherently smaller than  $W_{\rm dep}$ .

Fig. 9. Summary of the  $T_{\rm ch}$  dependencies of  $\Delta L$ ,  $\Delta L_{\rm SC}$ , and  $\Delta L_{\rm SBH}$ , where  $\Delta L = \Delta L_{\rm SC} + \Delta L_{\rm SBH}$ . The values of  $\Delta L_{\rm SC}$  and  $\Delta L_{\rm SBH}$  are estimated for qualitative understanding of their  $T_{\rm ch}$  dependencies and may involve some degree of inaccuracy.

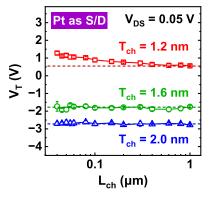

Interestingly,  $In_2O_3$  devices with Pt as S/D and  $T_{ch}$  = 1.2 nm exhibit an unusual  $V_T$  roll-up as the  $L_{ch}$  scales down (Fig. 11), which contrasts sharply with the typical  $V_T$  rolloff seen in the devices with Ni as S/D and  $T_{\rm ch}=1.2~{\rm nm}$ [Fig. 6(b)]. Normally, OSR dominates the influence of  $\Phi_{SR}$ on the CDE in In<sub>2</sub>O<sub>3</sub> transistors. However, with Pt as the S/D metal, where OSR is largely suppressed,  $\Phi_{SB}$  becomes the dominant factor affecting the  $V_T$ - $L_{ch}$  relationship. For  $T_{ch}$  = 1.2 nm devices, where  $\Phi_{SB} > 0$ , the upward band bending profile forms a depletion region and depletes electrons from the Pt/In<sub>2</sub>O<sub>3</sub> contact [Fig. 8(a)]. As the  $L_{ch}$  decreases, the depletion regions near the S/D start to influence the electron density at the In<sub>2</sub>O<sub>3</sub> channel center, resulting in the observed  $V_{\rm T}$  roll-up in Fig. 11. For  $T_{\rm ch} \geq 1.6$  nm devices, the negative  $\Phi_{\rm SB}$  with downward band bending has less effect on the  $V_{\rm T}$ - $L_{\rm ch}$  dependency (Fig. 11) because the accumulation region width  $[W_{acc}, as shown in Fig. 8(b)]$  is not long enough to affect the channel center when  $L_{\rm ch} \geq 40$  nm.

Fig. 10. Transfer characteristics of  $\ln_2 O_3$  transistors with Pt as the S/D metal, featuring  $L_{\rm ch}$  ranging from 1  $\mu{\rm m}$  to 40 nm and  $T_{\rm ch}$  of 1.2 nm [(a):  $I_{\rm D}$  in log scale; (d):  $I_{\rm D}$  in linear scale], 1.6 nm [(b):  $I_{\rm D}$  in log scale; (e):  $I_{\rm D}$  in linear scale], and 2.0 nm [(c):  $I_{\rm D}$  in log scale; (f):  $I_{\rm D}$  in linear scale]. Solid lines represent forward  $V_{\rm GS}$  sweeps, while dashed lines indicate backward sweeps. Compared to  $\ln_2 O_3$  FETs with Ni as the S/D metal (Fig. 2), devices using Pt exhibit a milder  $V_{\rm T}$  roll-off.

Fig. 11. Linearly extrapolated  $V_T$  as a function of  $L_{\rm ch}$  of  $\ln_2 O_3$  FETs with Pt as S/D and various  $T_{\rm ch}$ . Each data point represents the average of at least five devices.

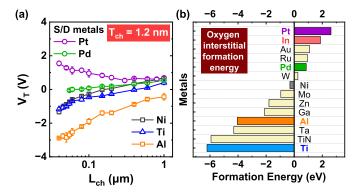

In addition to Pt and Ni, other metals, such as Al, Ti, and Pd, are also used as the S/D electrodes in In<sub>2</sub>O<sub>3</sub> transistors to investigate their impact on the  $V_T$  roll-off. Fig. 12(a) summarizes the  $V_T$ - $L_{ch}$  dependencies for  $In_2O_3$  FETs with these different S/D metals. Except for the devices using Pt as the S/D, all the other transistors exhibit significant  $V_T$  rolloff as the  $L_{ch}$  decreases. To understand these observations, the oxygen interstitial formation energies for various metals are simulated by ab initio calculations using QuantumATK, as shown in Fig. 12(b). The oxygen interstitial formation energy indicates how easily a material reacts with oxygen atoms: a lower formation energy suggests that the material is more likely to react with oxygen. Therefore, at the metal/In<sub>2</sub>O<sub>3</sub> interface, if the metal has a smaller oxygen interstitial formation energy than In, the oxygen atoms in In-O bonds will preferentially react with the metal, rather than staying in the

Fig. 12. (a) Linearly extrapolated  $V_T$  as a function of  $L_{\rm ch}$  for  $\ln_2 O_3$  FETs with various metals as S/D and  $T_{\rm ch}=1.2$  nm. Each data point represents the average of at least five devices. A broad range of metals were examined to assess their impact on the  $V_T$  roll-off in  $\ln_2 O_3$  transistors. (b) Simulated formation energies of oxygen interstitials in various metals. The energies were simulated by *ab initio* calculations using QuantumATK. Metals with smaller formation energies are more likely to react with oxygen.

In<sub>2</sub>O<sub>3</sub>, which leads to OSR. In Fig. 12(b), Pt is the only metal with a larger oxygen interstitial formation energy than In, meaning it does not scavenge oxygen from In<sub>2</sub>O<sub>3</sub>, and thus does not contribute to CDE and  $V_T$  roll-off. In contrast, metals like Pd, Ni, Al, and Ti have lower formation energies versus In, which facilitates the OSR at the metal/In<sub>2</sub>O<sub>3</sub> interface. The fact that many metals tend to have OSR with In-O bonds also explains why the  $V_T$  roll-off phenomenon is commonly observed not only in In<sub>2</sub>O<sub>3</sub> FETs [4], [22], [23], [24], [25] but also in other doped In<sub>2</sub>O<sub>3</sub> transistors like InSnO (ITO) [6], [26], IZO [18], IGO [12], and IGZO devices [9], [27], [31]. Notably, all these studies have used S/D metals (such as Ni, TiN, and Mo) with low oxygen interstitial formation energies.

### IV. CONCLUSION

In summary, this work systematically investigates the CDE and its impact on the  $V_T$  roll-off issue in  $In_2O_3$  FETs. The CDE describes the increase in carrier density near the S/D electrodes, forming n<sup>+</sup> regions, which leads to a non-uniform carrier concentration profile along the In<sub>2</sub>O<sub>3</sub> channel. By analyzing long  $L_{ch}$  and short  $L_{ch}$  devices separately, we extract  $R_{\text{sh},n}$ ,  $R_{\text{sh},+}$ , and  $\Delta L$  to quantify the CDE. The strong correlation between  $\Delta L$  and the  $L_{\rm ch}$  where  $V_{\rm T}$  roll-off begins suggests that the  $V_{\rm T}$  roll-off in  $\rm In_2O_3$  transistors is caused not by the traditional SCE but by the CDE. Next, the underlying mechanisms of the CDE are explored. It is found that the OSR that occurs when depositing the S/D metals on the In<sub>2</sub>O<sub>3</sub> channel is one of the reasons contributing to the CDE. The S/D metals may scavenge oxygen atoms from In<sub>2</sub>O<sub>3</sub>, generating oxygen vacancies and increasing the carrier density near the S/D. This OSR mechanism is verified through experiments with different S/D metals and simulations of oxygen interstitial formation energy. Additionally, the Schottky barrier height  $(\Phi_{SB})$  at the metal/ $In_2O_3$  contacts also has minor influences on the CDE. Positive  $\Phi_{SB}$  (when  $T_{ch} = 1.2$  nm) depletes carriers, while negative  $\Phi_{SB}$  (when  $T_{ch} \ge 1.6$  nm) accumulates carriers at the In<sub>2</sub>O<sub>3</sub> channel beneath the S/D electrodes. This research offers new insights into the CDE and its crucial role in the  $V_{\rm T}$  roll-off behavior of OS transistors. It lays the foundation for future studies aimed at mitigating CDE and improving the performance of  $\rm In_2O_3$  and other  $\rm In_2O_3$ -based transistors.

### REFERENCES

- [1] S. Datta, S. Dutta, B. Grisafe, J. Smith, S. Srinivasa, and H. Ye, "Back-end-of-line compatible transistors for monolithic 3D integration," *IEEE Micro*, vol. 39, no. 6, pp. 8–15, Nov. 2019, doi: 10.1109/MM.2019.2942978.

- [2] W. Chakraborty, B. Grisafe, H. Ye, I. Lightcap, K. Ni, and S. Datta, "BEOL compatible dual-gate ultra thin-body W-doped indium-oxide transistor with I<sub>on</sub> = 370μA/μm, SS = 73 mV/dec and I<sub>on</sub>/I<sub>off</sub> ratio >4×10<sup>9</sup>," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2, doi: 10.1109/VLSITECHNOLOGY18217.2020.9265064.

- [3] M. Si et al., "Why In<sub>2</sub>O<sub>3</sub> can make 0.7 nm atomic layer thin transistors," *Nano Lett.*, vol. 21, no. 1, pp. 500–506, Jan. 2021, doi: 10.1021/acs.nanolett.0c03967.

- [4] M. Si, A. Charnas, Z. Lin, and P. D. Ye, "Enhancement-mode atomic-layer-deposited In<sub>2</sub>O<sub>3</sub> transistors with maximum drain current of 2.2 A/mm at drain voltage of 0.7 V by low-temperature annealing and stability in hydrogen environment," *IEEE Trans. Electron Devices*, vol. 68, no. 3, pp. 1075–1080, Mar. 2021, doi: 10.1109/TED.2021.3053229.

- [5] M. Si, Z. Lin, Z. Chen, and P. D. Ye, "High-performance atomic-layer-deposited indium oxide 3D transistors and integrated circuits for monolithic 3D integration," *IEEE Trans. Electron Devices*, vol. 68, no. 12, pp. 6605–6609, Dec. 2021, doi: 10.1109/TED.2021.31 06282.

- [6] Z. Zhang et al., "Atomically thin indium-tin-oxide transistors enabled by atomic layer deposition," *IEEE Trans. Electron Devices*, vol. 69, no. 1, pp. 231–236, Jan. 2022, doi: 10.1109/TED.2021.3129707.

- [7] W. Tang et al., "Monolithic 3D integration of vertically stacked CMOS devices and circuits with high-mobility atomic-layer-deposited In<sub>2</sub>O<sub>3</sub> n-FET and polycrystalline Si p-FET: Achieving large noise margin and high voltage gain of 134 V/V," in *IEDM Tech. Dig.*, Dec. 2022, pp. 483–486, doi: 10.1109/IEDM45625.2022.10019410.

- [8] C. Niu et al., "Record-low metal to semiconductor contact resistance in atomic-layer-deposited In<sub>2</sub>O<sub>3</sub> TFTs reaching the quantum limit," in *IEDM Tech. Dig.*, Dec. 2023, pp. 1–4, doi: 10.1109/iedm45741.2023.10413708.

- [9] J. Zhang et al., "Back-end-of-line-compatible scaled InGaZnO transistors by atomic layer deposition," *IEEE Trans. Electron Devices*, vol. 70, no. 12, pp. 6651–6657, Dec. 2023, doi: 10.1109/TED.2023.33 12357

- [10] J. Zhang et al., "Fluorine anion-doped ultra-thin InGaO transistors overcoming mobility-stability trade-off," in *IEDM Tech. Dig.*, Dec. 2023, pp. 1–4, doi: 10.1109/iedm45741.2023.10413810.

- [11] J. Zhang et al., "First demonstration of BEOL-compatible atomic-layer-deposited InGaZnO TFTs with 1.5 nm channel thickness and 60 nm channel length achieving ON/OFF ratio exceeding 10<sup>11</sup>, SS of 68 mV/dec, normal-off operation and high positive gate bias stability," in *Proc. IEEE Symp. VLSI Technol. Circuits (VLSI Technol. Circuits)*, Jun. 2023, pp. 1–2, doi: 10.23919/VLSITECHNOLOGYAND-CIR57934.2023.10185312.

- [12] J. Zhang, D. Zheng, Z. Zhang, A. Charnas, Z. Lin, and P. D. Ye, "Ultrathin InGaO thin film transistors by atomic layer deposition," *IEEE Electron Device Lett.*, vol. 44, no. 2, pp. 273–276, Feb. 2023, doi: 10.1109/LED.2022.3233080.

- [13] Z. Zhang, Z. Lin, C. Niu, M. Si, M. A. Alam, and P. D. Ye, "Ultrahigh bias stability of ALD In<sub>2</sub>O<sub>3</sub> FETs enabled by high temperature O<sub>2</sub> annealing," in *Proc. IEEE Symp. VLSI Technol. Circuits (VLSI Technol. Circuits)*, Jun. 2023, pp. 1–2, doi: 10.23919/VLSITECHNOLOGYAND-CIR57934.2023.10185292.

- [14] C. Niu et al., "First demonstration of BEOL wafer-scale all-ALD channel CFETs using IGZO and Te for monolithic 3D integration," in *IEDM Tech. Dig.*, Dec. 2024, pp. 1–4, doi: 10.1109/iedm50854.2024.108 73541.

- [15] Z. Lin et al., "High-peformance BEOL-compatible atomic-layer-deposited In<sub>2</sub>O<sub>3</sub> Fe-FETs enabled by channel length scaling down to 7 nm: Achieving performance enhancement with large memory window of 2.2 V, long retention >10 years and high endurance >10<sup>8</sup> cycles," in *IEDM Tech. Dig.*, Dec. 2021, pp. 17.4.1–17.4.4, doi: 10.1109/IEDM19574.2021.9720652.

- [16] M. D. Bishop, H.-S. P. Wong, S. Mitra, and M. M. Shulaker, "Monolithic 3D integration," *IEEE Micro*, vol. 39, no. 6, pp. 16–27, Nov. 2019, doi: 10.1109/MM.2019.2942982.

- [17] D. Zheng, A. Charnas, J.-Y. Lin, J. Anderson, D. Weinstein, and P. D. Ye, "Ultrathin atomic-layer-deposited In<sub>2</sub>O<sub>3</sub> radio-frequency transistors with record high f<sub>T</sub> of 36 GHz and BEOL compatibility," in *Proc. IEEE Symp. VLSI Technol. Circuits (VLSI Technol. Circuits)*, Jun. 2023, pp. 1–2, doi: 10.23919/VLSITECHNOLOGYAND-CIR57934.2023.10185331.

- [18] D. Zheng et al., "First demonstration of BEOL-compatible ultrathin atomiclayer-deposited InZnO transistors with GHz operation and record high bias-stress stability," in *IEDM Tech. Dig.*, Dec. 2022, pp. 4.3.1–4.3.4, doi: 10.1109/IEDM45625.2022.10019452.

- [19] J. Xie et al., "Top-gate indium-tin-oxide power transistors featuring high breakdown voltage of 156 V," *IEEE Electron Device Lett.*, vol. 45, no. 10, pp. 1847–1850, Oct. 2024, doi: 10.1109/LED.2024.34 35428.

- [20] Z. Lin et al., "Enhancement of In<sub>2</sub>O<sub>3</sub> field-effect mobility up to 152 cm<sup>2</sup>.V<sup>-1</sup>.S<sup>-1</sup> using HZO-based higher-k linear dielectric," in *Proc. IEEE Symp. VLSI Technol. Circuits* (VLSI Technol. Circuits), Jun. 2024, pp. 1–2, doi: 10.1109/VLSITECHNOLOGYAND-CIR46783.2024.10631497.

- [21] Z. Zhang et al., "A gate-all-around In<sub>2</sub>O<sub>3</sub> nanoribbon FET with near 20 mA/m drain current," *IEEE Electron Device Lett.*, vol. 43, no. 11, pp. 1905–1908, Nov. 2022, doi: 10.1109/LED.2022.3210005.

- [22] C. Niu et al., "Surface accumulation induced negative Schottky barrier and ultralow contact resistance in atomic-layer-deposited In<sub>2</sub>O<sub>3</sub> thin-film transistors," *IEEE Trans. Electron Devices*, vol. 71, no. 5, pp. 3403–3410, May 2024, doi: 10.1109/TED.2024.33 67312.

- [23] Y.-Y. Pan et al., "Electronic impact of high-energy metal deposition on ultrathin oxide semiconductors," *Nano Lett.*, vol. 25, no. 7, pp. 2655–2661, Feb. 2025, doi: 10.1021/acs.nanolett.4c 05333.

- [24] A. Charnas, M. Si, Z. Lin, and P. D. Ye, "Enhancement-mode atomic-layer thin In<sub>2</sub>O<sub>3</sub> transistors with maximum current exceeding 2 A/mm at drain voltage of 0.7 V enabled by oxygen plasma treatment," *Appl. Phys. Lett.*, vol. 118, no. 5, Feb. 2021, Art. no. 052107, doi: 10.1063/5.0039783.

- [25] J.-Y. Lin et al., "Quantum confinement controlled positive to negative Schottky barrier conversion in ultrathin In<sub>2</sub>O<sub>3</sub> transistor contacts," in *IEDM Tech. Dig.*, Dec. 2024, pp. 1–4, doi: 10.1109/iedm50854.2024.10873514.

- [26] Y. Kang, K. Han, Y. Chen, and X. Gong, "Thickness-engineered extremely-thin channel high performance ITO TFTs with raised S/D architecture: Record-low R<sub>SD</sub>, highest mobility (sub-4 nm TCH regime), and high V<sub>TH</sub> tunability," in *Proc. IEEE Symp. VLSI Technol. Circuits* (VLSI Technol. Circuits), Jun. 2023, pp. 1–2, doi: 10.23919/VLSITECH-NOLOGYANDCIR57934.2023.10185421.

- [27] H. Tang et al., "Study of contact resistance components in short-channel indium-gallium-zinc-oxide transistor," *IEEE Trans. Electron Devices*, vol. 71, no. 1, pp. 567–573, Jan. 2024, doi: 10.1109/TED.2023.3332057.

- [28] R.-H. Yan, A. Ourmazd, and K. F. Lee, "Scaling the Si MOSFET: From bulk to SOI to bulk," *IEEE Trans. Electron Devices*, vol. 39, no. 7, pp. 1704–1710, Jul. 1992, doi: 10.1109/16.141237.

- [29] S. M. Sze, Y. Li, and K. K. Ng, Physics of Semiconductor Devices, 4th ed., Hoboken, NJ, USA: Wiley, 2021.

- [30] Z. Cheng et al., "How to report and benchmark emerging field-effect transistors," *Nature Electron.*, vol. 5, no. 7, pp. 416–423, Jul. 2022, doi: 10.1038/s41928-022-00798-8.

- [31] S. Lee, C. Niu, Y. Zhang, H. Wang, and P. Ye, "Positive to negative Schottky barrier transition in metal/oxide semiconductor contacts by tuning indium concentration in IGZO," in *Proc. IEEE Symp. VLSI Technol. Circuits (VLSI Technol. Circuits)*, Jun. 2024, pp. 1–2, doi: 10.1109/VLSITECHNOLOGYANDCIR46783.2024.10631411.

- [32] T. Kamiya and H. Hosono, "Material characteristics and applications of transparent amorphous oxide semiconductors," NPG Asia Mater., vol. 2, no. 1, pp. 15–22, Jan. 2010, doi: 10.1038/asiamat.2010.5.